Overview

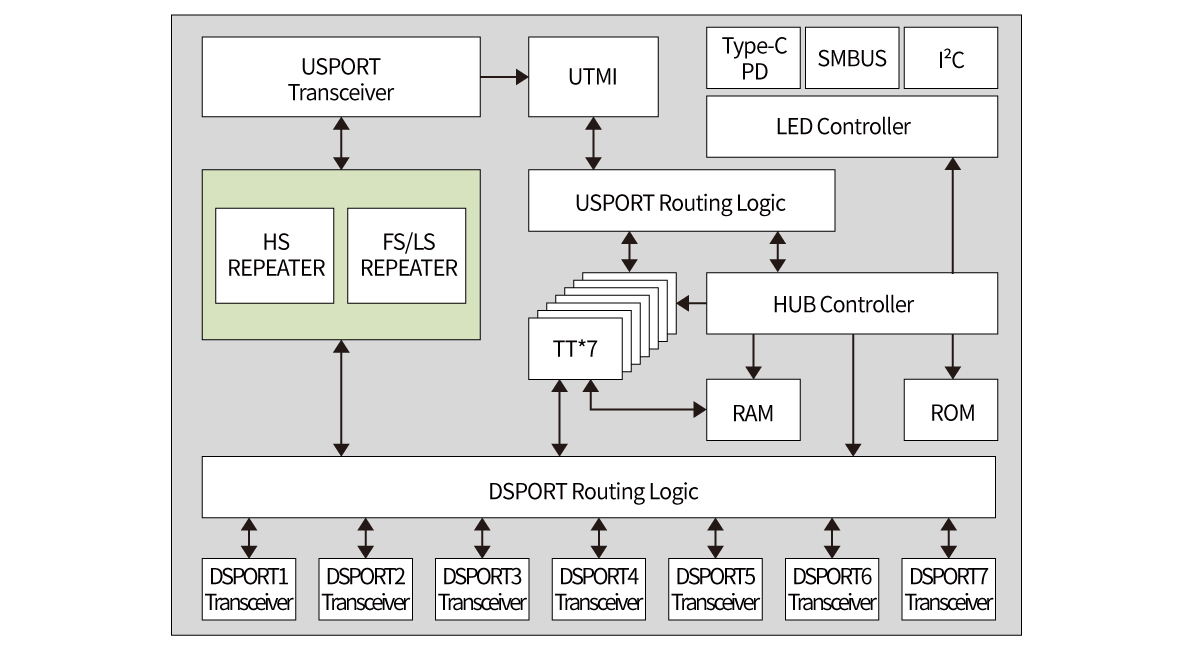

CH338 is a 7-port USB HUB controller chip that complies with the USB2.0 protocol specification. The upstream port supports USB2.0 high-speed and full-speed, the downstream port supports USB2.0 high-speed 480Mbps, full-speed 12Mbps and low-speed 1.5Mbps. It not only supports the low-cost STT mode (a single TT schedules 7 downstream ports in a time-sharing manner), but also supports the high-performance MTT mode (7 TTs each correspond to one port and are processed concurrently). In addition to the HUB controller function, some models also support PD function.

Industrial-grade design, streamlined peripherals, can be applied to computer and industrial computer motherboards, peripherals, embedded systems, etc.

Features

- 7-port USB HUB with 7 USB2.0 downstream ports, backward compatible with USB1.1 protocol specification

- Support independent power control for each port or GANG overall linkage power control

- Support independent over-current detection for each port or GANG overall over-current detection

- Support high-performance MTT mode, providing independent TT for each port to achieve full bandwidth concurrent transmission, the total bandwidth is 7 times that of STT

- Support port status LED indicator

- Whether to support composite devices, non-removable devices, custom VID, PID, port configuration and USB vender, product, serial number string descriptors, etc. can be configured through external EEPROM or internal EEPROM.

- Chip related parameters can be configured through the SMBus interface

- Built-in information memory, vender or product information and configuration can be customized in batches according to special needs of the industry

- Self-developed dedicated USBPHY, low-power consumption technology, supports self-power supply or bus power supply

- Functions such as self-powered or bus-powered modes can be configured through I/O pins

- Provide crystal oscillator, built-in capacitor, supports external clock input, built-in PLL provides 480MHz clock for USBPHY

- Some applications can support crystal-free mode, saving external crystals and capacitors.

- The upstream port has a built-in 1.5KΩ pull-up resistor, and the downstream port has a built-in pull-down resistor required by the USB Host, simplifying the peripherals.

- Some models have a built-in LDO linear step-down regulator, which can convert the USB bus power supply voltage into the chip’s 3.3V working power supply.

- 6KV Enhanced ESD Performance, Class 3A

- Industrial grade temperature range: -40 to 85°C

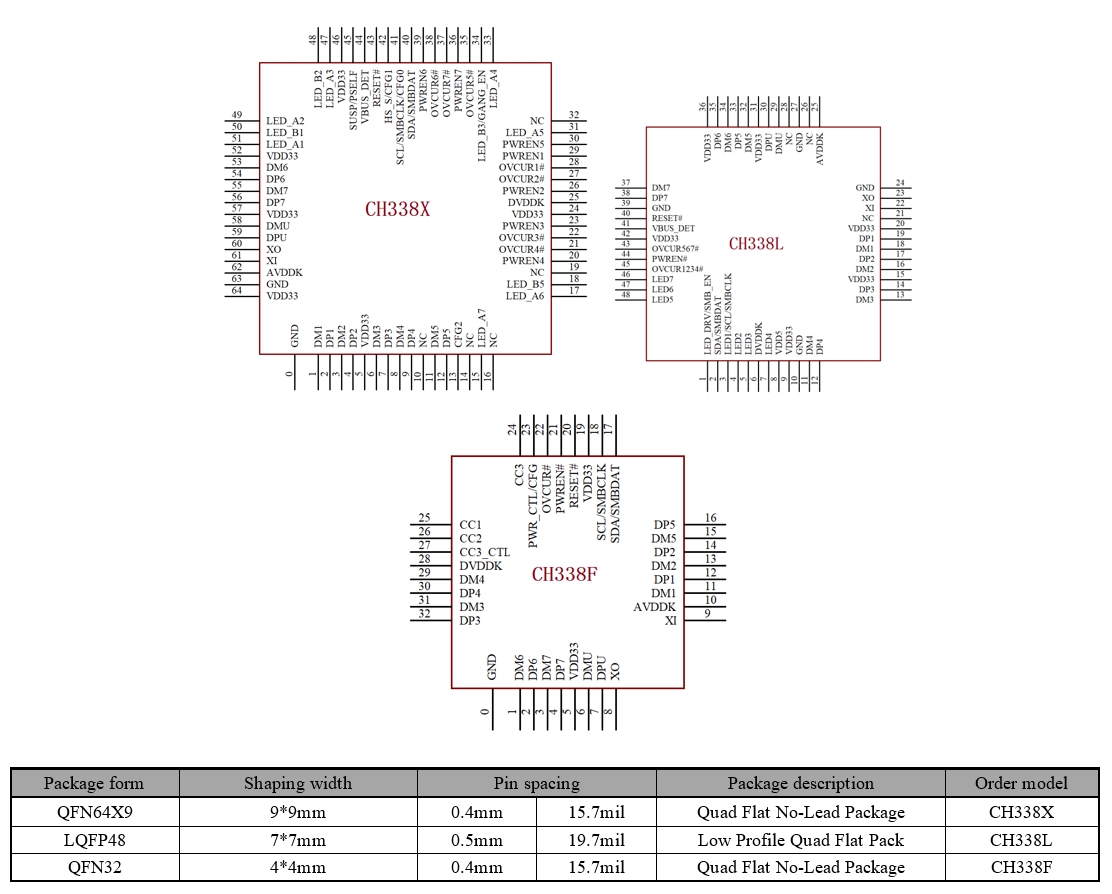

- Available in QFN64X9, LQFP48, QFN32 and other small, low-cost, easy-to-process packages

Package

Note: CH338F is preferred for small size; CH338X and CH338L focus on PCB compatibility.

Note: CH338F is preferred for small size; CH338X and CH338L focus on PCB compatibility.

Pin 0# is the EPAD of the QFN package and is a required connection.