Overview

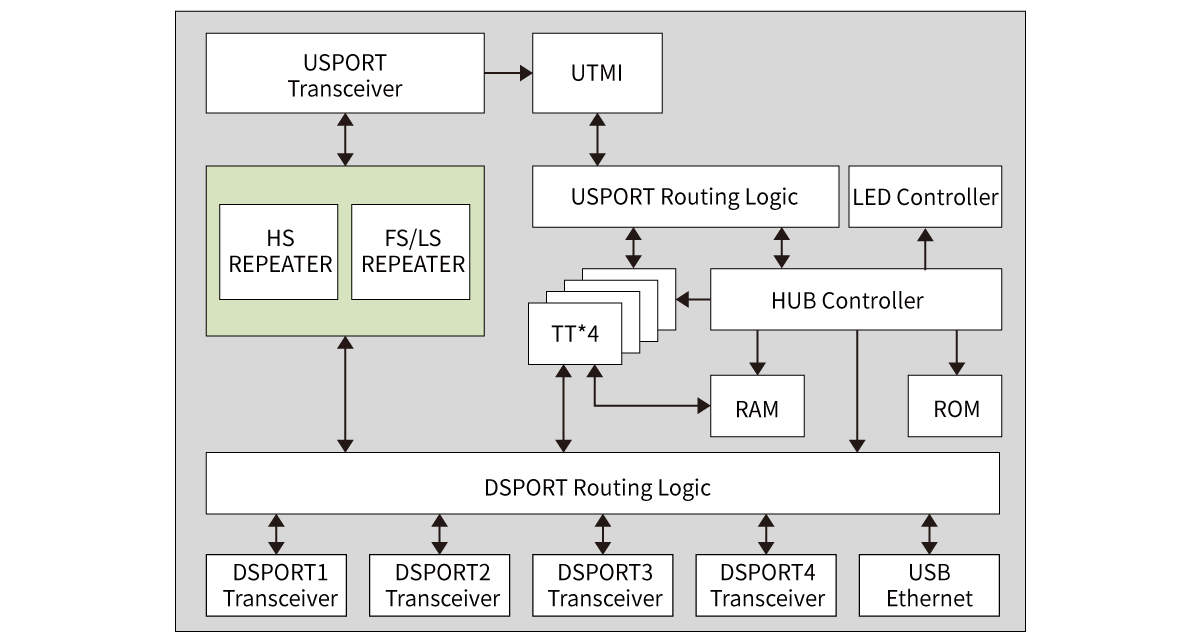

CH336 is a 4-port HUB and USB to Ethernet 2-in-1 controller chip compliant with USB2.0 protocol specification, which integrates 4-port USB HUB and USB 100 Gigabit Ethernet expansion functions in a single chip. CH336 upstream port supports USB high-speed and full-speed, downstream port supports USB2.0 high-speed 480Mbps, full-speed 12Mbps and low-speed 1.5Mbps, provides fast direct transmission channel for USB NIC in HUB, and Ethernet supports 10M/100M automatic negotiation to automatically identify positive and negative signal lines. CH336 supports high performance MTT mode, streamlined peripherals, and can be applied to computer and industrial controller motherboards, peripherals, embedded systems and other scenarios.

Features

USB HUB

- 4-port USB HUB, provide 4 USB2.0 downstream port, downwards compatible with USB1.1 protocol specifications

- Support high-performance MTT mode and provide independent TT for each port to achieve full-bandwidth concurrent transmission. The total bandwidth is 4 times that of STT.

- Self-developed dedicated USBPHY, low-power consumption technology, support self-power supply or bus power supply

- Provide crystal oscillator, support external clock input, built-in PLL provides 480MHz clock for USB PHY

- Non-Ethernet applications can support crystal-free mode, saving external crystals and capacitors

- The upstream port has built-in 1.5KΩ pull-up resistor, and the downstream port has built-in pull-down resistance required by the USB Host,streamlined peripherals.

USB Extended NIC

- Built-in self-developed 10M/100M Ethernet MAC+PHY, compatible with IEEE 802.3 10BASE-T/100BASE-TX

- Support CDC-ECM and CDC-NCM protocols, no installation of drivers or optional vendor drivers

- 10M/100M automatic negotiation, support UTP CAT5E, CAT6, support Auto-MDIX, automatically identify positive and negative signal lines

- Support hibernation mode and low-power sleep mode, support network low-power configuration and dynamic power management

- Support remote wake-up through events such as magic packets and network wake-up packets

- Support IPv4/IPv6 packet verification, IPv4 TCP/UDP/HEAD and IPv6 TCP/UDP packet verification generation and inspection

Other Features

- Built-in information memory, mass customization of manufacturer or product information and configuration according to the special needs of the industry

- Processor core, high-speed USB, Ethernet and other controllers and PHY transceiver IP is fully self-developed, each module is tightly coordinated, high efficiency and low cost, eliminating IP license fees.

- The built-in LDO linear step-down regulator can convert the USB bus power supply voltage into the 3.3V working power supply of the chip.

- Provide QSOP24 and other packaging forms with small size, low cost and easy-to-process.

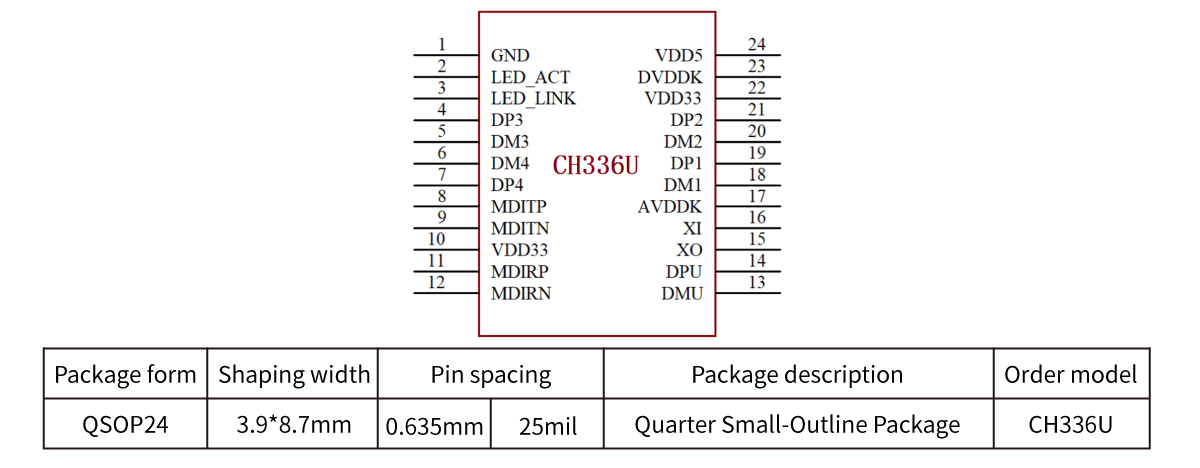

Package